Performance Evaluation for Stacked-Layer Data Bus Based on Isolated Unit-Size Repeater Insertion

Keywords:

stacked-layer chip, 3D data bus, unit-size repeater, average access timeAbstract

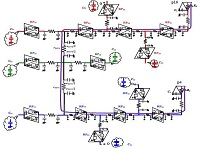

The data bus of a stacked-layer chip always supports that data of a program are frequently running on the bus at different timing periods. The average data access time of a data bus to the timing periods dominates the program performance. In this paper, we proposed an evaluated approach to reconstruct a 3D data bus with inserted unit-size repeaters to motivate that the average data access time of the bus on a complete timing period can speed up at least 10%. The approach is trying to insert a number of unit-size repeaters into bus wires along the path of a source-sink pair for isolating extra capacitive loadings at each timing period to reduce their access time. The above process is repeated until no any improvement for each access time. Each inserted repeater with just one unit size due to the limited space of a chip area and the minor reconstruction of a data bus in practical. The approach has the advantages of uniform repeater insertion, less extra area occupation, and simplified time-to-space tradeoff. Experimental results show that our approach has the rapid capable evaluation for a stacked-layer data bus within one millisecond and the saving in average access time is up to 50.81% with the inserted repeater sizes of 70 on average.

References

EE Times, The state of the art in 3D IC technologies, November 27, 2013.

Y. I. Ismail, E. G. Friedman, and J. L. Neves, “Repeater insertion in tree structured inductive interconnect,” IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 48, no. 5, pp.471-481, May 2001.

K. Y. Lin, H. T. Lin, T. Y. Ho, and C. C. Tsai, “Load-balanced clock tree synthesis with adjustable delay buffer insertion for clock skew reduction in multiple dynamic supply Voltage designs,” ACM Trans. on Design Automation of Electronic Systems, vol. 17, no. 3, Article 34, 2012.

M. Ghoneima and Y. Ismail, “Optimum positioning of interleaved repeaters in bidirectional buses,” IEEE Trans. on CAD of Integrated Circuits and Systems, vol. 24, no. 3, pp. 461-669, March 2005.

Q. Ashton Acton, Issues in Electronic Circuits, Devices, and Materials: 2011 Edition, Scholarly Editions, January 2012.

M. Daneshtalab, M. Ebrahimi, and J. Plosila, “HIBS- Novel inter-layer bus structure for stacked architectures,” Proc. IEEE International Conference on 3D System Integration (3DIC 12), February 2012, pp. 1-7.

I. G. Thakkar and S. Pasricha, “3D-Wiz: A novel high bandwidth, optically interfaced 3D DRAM architecture with reduced random access time,” Proc. IEEE International Conference on Computer Design (ICCAD 14), November 2014, pp. 1-7.

K. Cho, H. S. Na, T. W. Cho, and Y. You, “Analysis of system bus on SoC platform using TSV interconnection,” Proc. IEEE Asia Symposium on Quality Electronic Design (ASQED 12), August 2012, pp. 255-259.

K. S. Mohamed, IP cores design from specifications to production, Chap-4 SoC buses and peripherals, 1st ed. Switzerland: Springer International Publishing, 2016.

S. Khan, S. Anjum, U. A. Gulzari, and F. S. Torres, “Comparative analysis of network-on-chip simulation tools,” IET Computers & Digital Techniques, vol. 12, no. 1, pp. 30-38, January 2018.

C. C. Tsai, “Repeater insertion for 3D data bus with TSVs for reducing critical propagation delay,” Proc. International Conference on Computer Science and Information Engineering (CSIE 15), June 2015, pp. 203-208.

C. C. Tsai, “An effective algorithm for minimizing the critical access time of a 3D-chip data bus,” International Journal of Electronics Communication and Computer Engineering, vol. 9, no. 4, pp. 117-123, July 2018.

C. C. Tsai, “Embedded bus switches on 3D data bus for critical access time reduction,” Proc. IEEE Latin American Symposium on Circuits and Systems (LASCAS 18), February 2018, pp. 1-4.

IDTQS3245 data sheet, IDT Co., November 2014.

74VHCT126AFT data sheet, Toshiba Co., November 2014.

C. C. Tsai, D. Y. Kao, and C. K. Cheng, “Performance driven bus buffer insertion,” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol. 15, no. 4, pp. 429-437, April 1996.

W. C. Elmore, “The transient response of damped linear networks,” Journal of Applied Physics, vol. 19, no. 1, pp. 55-63, January 1948.

T. Bandyopadhyay, K. J. Han, D. Chung, R. Chatterjee, M. Swaminathan, and R. Tummala, “Rigorous electrical modeling of through silicon vias with MOS capacitance effects,” IEEE Trans. Components, Packaging, and Manufacturing Technology, vol. 1, no. 6, pp. 893-903, June 2011.

Y. Cao, W. Zhao, E. Wang, W. Wang, J. Velamala, A. Balijepali, and S. Sinha, "Predictive Technology Model (PTM)," http://ptm.asu.edu, June 1, 2012.

Published

How to Cite

Issue

Section

License

Submission of a manuscript implies: that the work described has not been published before that it is not under consideration for publication elsewhere; that if and when the manuscript is accepted for publication. Authors can retain copyright in their articles with no restrictions. is accepted for publication. Authors can retain copyright of their article with no restrictions.

Since Jan. 01, 2019, AITI will publish new articles with Creative Commons Attribution Non-Commercial License, under The Creative Commons Attribution Non-Commercial 4.0 International (CC BY-NC 4.0) License.

The Creative Commons Attribution Non-Commercial (CC-BY-NC) License permits use, distribution and reproduction in any medium, provided the original work is properly cited and is not used for commercial purposes.