Analysis of Drain-Induced Barrier Lowering for Gate-All-Around FET with Ferroelectric

DOI:

https://doi.org/10.46604/ijeti.2023.12887Keywords:

gate-all-around, DIBL, ferroelectric, remanent polarization, coercive fieldAbstract

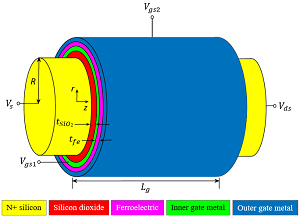

This study presents an analytical model for the drain-induced barrier lowering (DIBL) of a junctionless gate-all-around FET with ferroelectric, utilizing a 2D potential model. A multilayer structure of metal-ferroelectric-metal-insulator-semiconductor is used as the gate, as well as the remanent polarization and coercive field values corresponding to HZO are used. The DIBLs obtained with the proposed model demonstrate good agreement with those obtained using the second derivative method, which relies on the 2D relationship between drain current and gate voltage. The results demonstrate that an increase in ferroelectric thickness leads to a negative DIBL value due to the ferroelectric charge. Additionally, there exists an inverse relationship between ferroelectric thickness and channel length to achieve a DIBL value of 0. This condition is satisfied only with the increase of the ferroelectric thickness as the channel radius and insulator thickness increase. The DIBLs increase with higher remanent polarization and lower coercive field, remaining constant when the ratio of remanent polarization and coercive field is maintained.

References

I. Luk’yanchuk, A. Razumnaya, A. Sene, Y. Tikhonov, and V. M. Vinokur, “The Ferroelectric Field-Effect Transistor with Negative Capacitance,” npj Computational Materials, vol. 8, article no. 52, 2022.

J. F. Yao, X. Han, X. P. Zhang, J. C. Liu, M. Y. Gu, M. L. Zhang, et al., “Investigation on the Negative Capacitance Field Effect Transistor with Dual Ferroelectric Region,” Crystals, vol. 12, no. 11, article no. 1545, November 2022.

S. Yadav, S. Rewari, and R. Pandey, “Impact of Temperature on a Ferroelectric Interfaced Negative Capacitance Double Gate Junctionless Accumulation Mode Field Effect Transistor-Compact Model,” Proceedings of the Royal Society A, vol. 479, no. 2271, article no. 20220528, March 2023.

Malvika, B. Choudhuri, and K. Mummaneni, “A Review on a Negative Capacitance Field-Effect Transistor for Low-Power Applications,” Journal of Electronic Materials, vol. 51, no. 3, pp.923-937, March 2022.

M. B. M. Hashim, A. Z. Alam, and N. B. Darmis, “Effect of Ferro Electric Thickness on Negative Capacitance FET (NCFET),” IIUM Engineering Journal, vol. 22, no. 1, pp.339-346, January 2021.

F. I. Sakib, M. A. Hasan, and M. Hossain, “Performance Analysis of Nanowire and Nanosheet NCFETs for Future Technology Nodes,” Engineering Research Express, vol. 3, no. 4, article no. 045044, December 2021.

F. I. Sakib, M. A. Hasan, and M. Hossain, “Exploration of Negative Capacitance in Gate-All-Around Si Nanosheet Transistors,” IEEE Transactions on Electron Devices, vol. 67, no. 11, pp. 5236-5242, November 2020.

K. T. Chen, S. S. Gu, Z. Y. Wang, C. Y. Liao, Y. C. Chou, R. C. Hong, et al., “Ferroelectric HfZrOx FETs on SOI Substrate with Reverse-DIBL (Drain-Induced Barrier Lowering) and NDR (Negative Differential Resistance),” IEEE Journal of the Electron Devices Society, vol. 6, pp. 900-904, August 2018.

H. Jung, “Analysis of Drain Induced Barrier Lowering for Junctionless Double Gate MOSFET Using Ferroelectric Negative Capacitance Effect,” AIMS Electronics and Electrical Engineering, vol. 7, no. 1, pp. 38-49, 2023.

J. P. Duarte, S. Khandelwal, A. I. Khan, A. Sachid, Y. K. Lin, H. L. Chang, et al., “Compact Models of Negative-Capacitance FinFETs: Lumped and Distributed Charge Models,” IEEE International Electron Devices Meeting, pp. 30.5.1-30.5.4, December 2016.

A. Rassekh, J. M. Sallese, F. Jazaeri, M. Fathipour, and A. M. Ionescu, “Negative Capacitance Double-Gate Junctionless FETs: A Charge-Based Modeling Investigation of Swing, Overdrive and Short Channel Effect,” IEEE Journal of the Electron Devices Society, vol. 8, pp. 939-947, September 2020.

B. Awadhiya, P. N. Kondekar, S. Yadav, and P. Upadhyay, “Insight into Threshold Voltage and Drain Induced Barrier Lowering in Negative Capacitance Field Effect Transistor,” Transactions on Electrical and Electronic Materials, vol. 22, no. 3, pp. 267-273, June 2021.

A. K. Saha, P. Sharma, I. Dabo, S. Datta, and S. K. Gupta, “Ferroelectric Transistor Model Based on Self-Consistent Solution of 2D Poisson’s, Non-Equilibrium Green’s Function and Multi-Domain Landau Khalatnikov Equations,” IEEE International Electron Devices Meeting, pp. 13.5.1-13.5.4, December 2017.

S. Chaudhary, B. Dewan, C. Sahu, and M. Yadav, “Effect of Negative Capacitance in Partially Ground Plane Based SELBOX FET on Capacitance Matching and SCEs,” Silicon, vol. 14, pp. 7099-7108, 2022.

C. C. Lee, D. R. Hsieh, S. W. Li, Y. S. Kuo, and T. S. Chao, “Hysteresis-Free Gate-All-Around Stacked Poly-Si Nanosheet Channel Ferroelectric HfxZr1-xO2 Negative Capacitance FETs with Internal Metal Gate and NH3 Plasma Nitridation,” IEEE Transactions on Electron Devices, vol. 69 no. 3, pp. 1512-1518, March 2022.

S. Y. Lee, C. C. Lee, Y. S. Kuo, S. W. Li, and T. S. Chao, “Ultrathin Sub-5-nm Hf1₋xZrxO2 for a Stacked Gate-All-Around Nanowire Ferroelectric FET with Internal Metal Gate,” IEEE Journal of the Electron Devices Society, vol. 9, pp. 236-241, February 2021.

L. Qin, C. Li, Y. Wei, G. Hu, J. Chen, Y. Li, et al., “Recent Developments in Negative Capacitance Gate-All-Around Field Effect Transistors: A Review,” IEEE Access, vol. 11, pp. 14028-14042, February 2023.

B. Liu, Y. Zhang, L. Zhang, Q. Yuan, W. Zhang, and Y. Li, “Excellent HZO Ferroelectric Thin Films on Flexible PET Substrate,” Journal of Alloys and Compounds, vol. 919, article no. 165872, October 2022.

A. J. Cho. J. Jeon, H. K. Chung, I. H. Baek, K. Yang, M. H. Park, et al., “Effects of Oxygen Sources on Properties of Atomic-Layer-Deposited Ferroelectric Hafnium Zirconium Oxide Thin Films,” Ceramics International, vol. 48, no. 3, pp. 3280-3286, February 2022.

C. Li, Y. Zhuang, S. Di, and R. Han, “Subthreshold Behavior Models for Nanoscale Short-Channel Junctionless Cylindrical Surrounding-Gate MOSFETs,” IEEE Transactions on Electron Devices, vol. 60, no. 11, pp. 3655-3662, November 2013.

F. Jazaeri, N. Makris, A. Saeidi, M. Bucher, and J. M. Sallese, “Charge-Based Model for Junction FETs,” IEEE Transactions on Electron Devices, vol. 65 no. 7, pp. 2694-2698, July 2018.

R. Rasool, N. Din, and G. M. Rather, “Analytical Model for the Effects of the Variation of Ferrolectric Material Parameters on the Minimum Subthreshold Swing in Negative Capacitance Capacitor,” Journal of Semiconductors, vol. 40, no. 12, article no. 122401, December 2019.

H. Jung, “Impact of Gate Metal Work-Function for On-to-Off Current Ratio and Threshold Voltage in Junctionless Gate-All-Around (GAA) MOSFET Stacked with SiO2 and High-k Dielectric,” International Journal of Emerging Technology and Advanced Engineering, vol. 13, no. 1, pp. 124-132, January 2023.

A. Ortiz-Conde, F. J. Garcia-Sanchez, J. Muci, A. T. Barrios, J. J. Liou, and C. S. Ho, “Revisiting MOSFET Threshold Voltage Extraction Methods,” Microelectronics Reliability, vol. 53, no. 1, pp. 90-104, January 2013.

H. Jung, “Analysis of Drain Induced Barrier Lowering for Junctionless Double Gate MOSFET Using Ferroelectric Negative Capacitance Effect,” AIMS Electronics and Electrical Engineering, vol. 7, no. 1, pp. 38-49, 2023.

H. Jiao, X. Wang, S. Wu, Y. Chen, J. Chu, and J. Wang, “Ferroelectric Field Effect Transistors for Electronics and Optoelectronics,” Applied Physics Reviews, vol. 10, no. 1, article no. 011310, March 2023.

H. Jung, “Analytical Model of Subthreshold Swing in Junctionless Gate-All-Around (GAA) FET with Ferroelectric,” AIMS Electronics and Electrical Engineering, vol. 7, no. 4, pp. 322-336, 2023.

W. Huang, H. Zhu, Y. Zhang, Z. Wu, K. Jia, X. Yin, et al., “Investigation of Negative DIBL Effect for Ferroelectric-Based FETs to Improve MOSFETs and CMOS Circuit,” Microelectronics Journal, vol. 114, article no. 105110, August 2021.

Published

How to Cite

Issue

Section

License

Copyright (c) 2024 Hakkee Jung

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.

Copyright Notice

Submission of a manuscript implies: that the work described has not been published before that it is not under consideration for publication elsewhere; that if and when the manuscript is accepted for publication. Authors can retain copyright in their articles with no restrictions. Also, author can post the final, peer-reviewed manuscript version (postprint) to any repository or website.

Since Jan. 01, 2019, IJETI will publish new articles with Creative Commons Attribution Non-Commercial License, under Creative Commons Attribution Non-Commercial 4.0 International (CC BY-NC 4.0) License.

The Creative Commons Attribution Non-Commercial (CC-BY-NC) License permits use, distribution and reproduction in any medium, provided the original work is properly cited and is not used for commercial purposes.

.jpg)